#### WASHINGTON UNIVERSITY IN ST. LOUIS

McKelvey School of Engineering

Department of Computer Science & Engineering

Dissertation Examination Committee:

Roger Chamberlain, Chair

Ron Cytron

Chris Gill

Tim York

Xuan Zhang

Multi-Layer Support for Component-Based Cyber-Physical Systems Applications by Oren Bell

A dissertation presented to the McKelvey School of Engineering of Washington University in partial fulfillment of the requirements for the degree of Doctor of Philosophy

> August 2025 St. Louis, Missouri

# Table of Contents

| List of          | Figur         | es                                                      | v    |

|------------------|---------------|---------------------------------------------------------|------|

| List of          | Table         | es                                                      | vii  |

| Ackno            | wledgr        | ments                                                   | viii |

| Abstra           | act           |                                                         | ix   |

| $\mathbf{Chapt}$ | er 1: I       | Introduction                                            | 1    |

| 1.1              | ROS 2         | 2                                                       | . 3  |

| 1.2              |               | minary Work                                             |      |

| $\mathbf{Chapt}$ | er 2: Z       | Zero-Copy Memory Management for Heterogeneous Computing | g 9  |

| 2.1              | Hazca         | at                                                      | . 12 |

|                  | 2.1.1         | Heterogeneity Aware Allocator                           |      |

|                  | 2.1.2         | Message Queue                                           |      |

|                  | 2.1.3         | Message Lifecycle                                       |      |

|                  | 2.1.4         | Design and Implementation                               |      |

|                  | 2.1.5         | Empirical Evaluation                                    |      |

|                  | 2.1.6         | Conclusions and Future Work                             |      |

| 2.2              | Alloca        | ators for Device Memory                                 |      |

|                  | 2.2.1         | Background and Related Work                             |      |

|                  | 2.2.2         | Alternatives to Free Lists                              |      |

|                  | 2.2.3         | Sequential Algorithms                                   |      |

|                  | 2.2.4         | Segregation Algorithms                                  |      |

|                  | 2.2.5         | Evaluation                                              |      |

|                  | 2.2.6         | Conclusion                                              |      |

| Chant            | er 3· F       | ROS 2 Scheduler                                         | 52   |

| 3.1              |               | nciling ROS 2 with Classical Real-Time                  | 02   |

| 5.1              |               | luling of Periodic Tasks                                | . 53 |

|                  | 3.1.1         | Classical Schedulers and Executors in ROS 2             |      |

|                  | 3.1.1 $3.1.2$ | The Events Executor                                     |      |

|                  | _             |                                                         |      |

|                  | 3.1.3         | Problem Definition                                      | . თა |

|                  | 3.1.4   | Proposed Scheduler                                                 |

|------------------|---------|--------------------------------------------------------------------|

|                  | 3.1.5   | Compatibility with Non-Preemptive Schedulers for Periodic Tasks 68 |

|                  | 3.1.6   | Subscription Tasks                                                 |

|                  | 3.1.7   | Evaluation                                                         |

|                  | 3.1.8   | Conclusion                                                         |

| 3.2              | Graph   | -Aware Scheduling in ROS 2                                         |

|                  | 3.2.1   | System Model                                                       |

|                  | 3.2.2   | Mapping ROS 2 to DAG Task Model                                    |

|                  | 3.2.3   | Graph Unfolding                                                    |

|                  | 3.2.4   | Fusion Nodes                                                       |

|                  | 3.2.5   | Executor Design                                                    |

|                  | 3.2.6   | Analysis                                                           |

|                  | 3.2.7   | Extension to non-LIFO queues                                       |

|                  | 3.2.8   | Evaluations                                                        |

|                  | 3.2.9   | Conclusions and Future Work                                        |

| 3.3              | Comm    | nentary on Multi-threaded Schedulers                               |

|                  | 3.3.1   | The Information Erasure Problem                                    |

|                  | 3.3.2   | Mutual Exclusion and Schedulability                                |

|                  | 3.3.3   | Research Scope                                                     |

| 3.4              | Concl   | <u></u>                                                            |

|                  |         |                                                                    |

| $\mathbf{Chapt}$ | er 4: S | tate Estimator Handoffs in Safety-Critical Systems 105             |

| 4.1              | Prelim  | ninary Work                                                        |

|                  | 4.1.1   | DYFC BLAS Performance                                              |

| 4.2              |         | uction                                                             |

| 4.3              | _       | round                                                              |

|                  | 4.3.1   | Kalman Filter                                                      |

|                  | 4.3.2   | Extended Kalman Filter                                             |

|                  | 4.3.3   | Unscented Kalman Filter                                            |

|                  | 4.3.4   | Particle Filter                                                    |

| 4.4              |         | n Model                                                            |

|                  | 4.4.1   | System Definition                                                  |

|                  | 4.4.2   | Reachable Sets                                                     |

|                  | 4.4.3   | Requirements for System                                            |

| 4.5              | Enforc  | cing Safety                                                        |

|                  | 4.5.1   | Construction of Barrier Certificates                               |

|                  | 4.5.2   | Linear Region                                                      |

|                  | 4.5.3   | Transitioning to Nonlinear                                         |

|                  | 4.5.4   | Transitioning to Linear                                            |

|                  | 4.5.5   | Computing Reachable Sets                                           |

| 4.6              | Applie  | eation to State Estimators                                         |

|                  | 4.6.1   | Control Semantics                                                  |

|                  | 4.6.2   | Scheduling Semantics                                               |

| 4.7    | Conclusions and Future Work | 32         |

|--------|-----------------------------|------------|

| Refere | nces                        | 35         |

| Appen  | lix A: Hybrid-Array Lists   | <b>4</b> 6 |

| A.1    | Insert                      | 47         |

| A.2    | Remove                      | 47         |

| A.3    | Search                      | 47         |

| A.4    | Iterators                   | 48         |

# List of Figures

| Figure 1.1:  | Dissertation layers                                                                                       | 2  |

|--------------|-----------------------------------------------------------------------------------------------------------|----|

| Figure 1.2:  | ROS 2 stack [61]                                                                                          | 4  |

| Figure 1.3:  | Cinematography Application [23]                                                                           | 6  |

| Figure 1.4:  | Still frames from Deer Stalker Application                                                                | 7  |

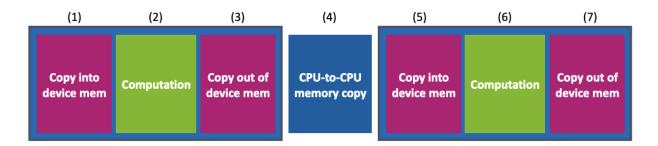

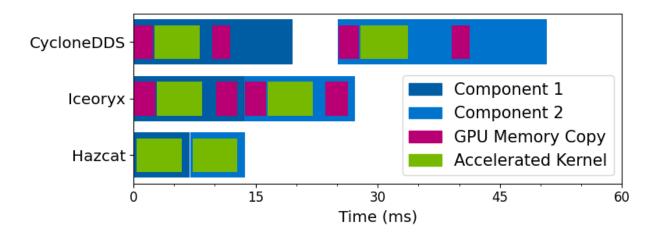

| Figure 2.1:  | Time sequence illustrating communication between two hardware accelerated components                      | 11 |

| Figure 2.2:  | Structure of allocator and partitions (not to scale)                                                      | 16 |

| Figure 2.3:  | Stacktrace Sampling                                                                                       | 26 |

| Figure 2.4:  | Two Component Experiment with Hardware Acceleration                                                       | 27 |

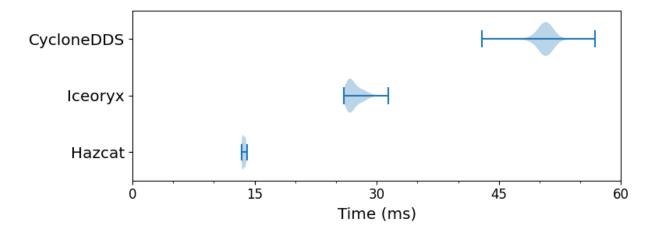

| Figure 2.5:  | End-to-end Latency Distributions for Two Component Experiment                                             | 28 |

| Figure 2.6:  | Relative performance with randomized ROS graphs                                                           | 29 |

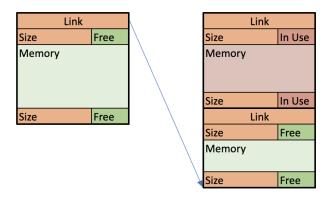

| Figure 2.7:  | Demonstration of Boundary Tags                                                                            | 39 |

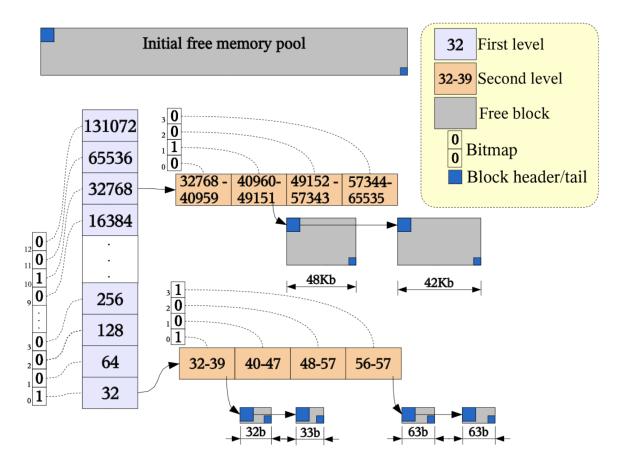

| Figure 2.8:  | TLSF Data Structure [87]                                                                                  | 49 |

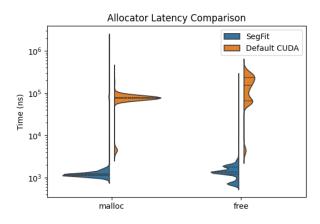

| Figure 2.9:  | Latency of malloc and free                                                                                | 50 |

| Figure 2.10: | Memory usage during benchmark                                                                             | 50 |

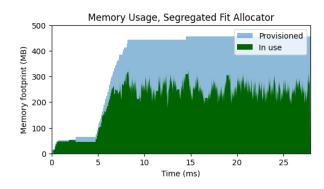

| Figure 3.1:  | Scheduling mechanisms                                                                                     | 55 |

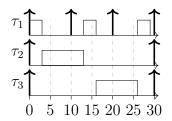

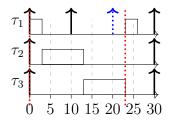

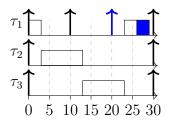

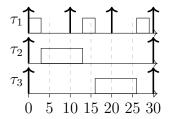

| Figure 3.2:  | Schedules for the running example of Section 3.1.1                                                        | 57 |

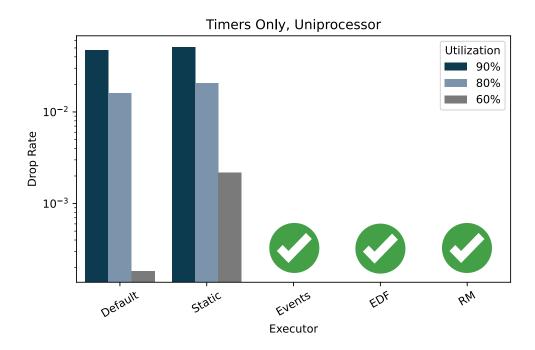

| Figure 3.3:  | Dropped jobs on timer-only task sets: A checkmark indicates no dropped jobs across all utilization levels | 77 |

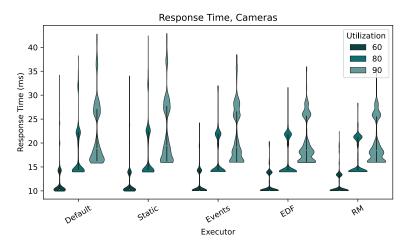

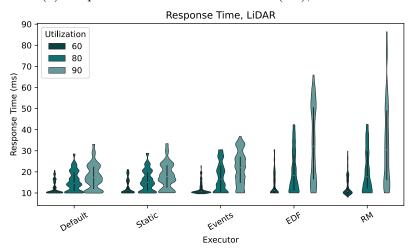

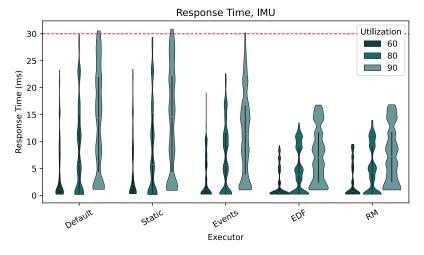

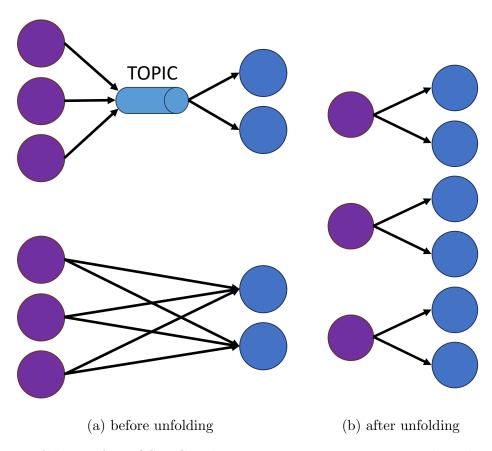

| Figure 3.4:  | Response Time of Tasks (ms)                                                                                                                                                                                                          | 80  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

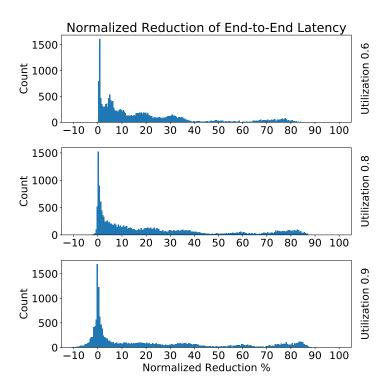

| Figure 3.5:  | Reduction of the end-to-end latency between the default ROS 2 executor and our RM events executor                                                                                                                                    | 82  |

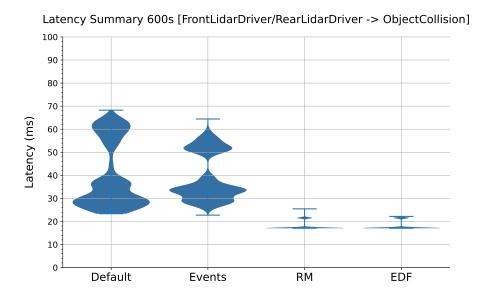

| Figure 3.6:  | End-to-end latency of the hot path in the Autoware reference system under different executors                                                                                                                                        | 83  |

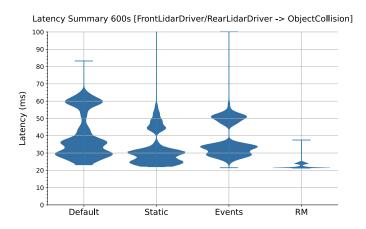

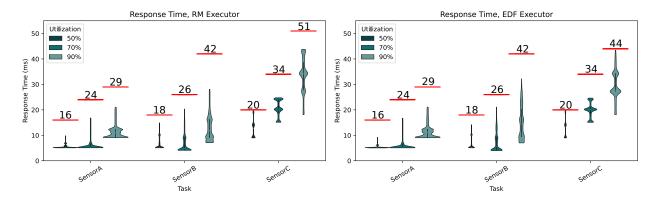

| Figure 3.7:  | Unfolding of a ROS 2 Graph into a Forest. Timers in purple, subscriptions in blue                                                                                                                                                    | 89  |

| Figure 3.8:  | Response times for the synthetic task set compared against the WCRT bounds from analysis [92]. Task A, B, and C correspond to the root tasks with periods 25ms, 41ms, and 51ms, respectively. Red lines indicate the analytical WCRT | 98  |

| Figure 3.9:  | Autoware Reference Benchmark Executor Comparison                                                                                                                                                                                     | 99  |

| Figure 3.10: | Unfolding of a ROS 2 graph with locks. Callbacks in the same mutual exclusion group (see nodes B and C) are modeled with a shared lock that is passed to their virtual copies created during graph unfolding                         | 102 |

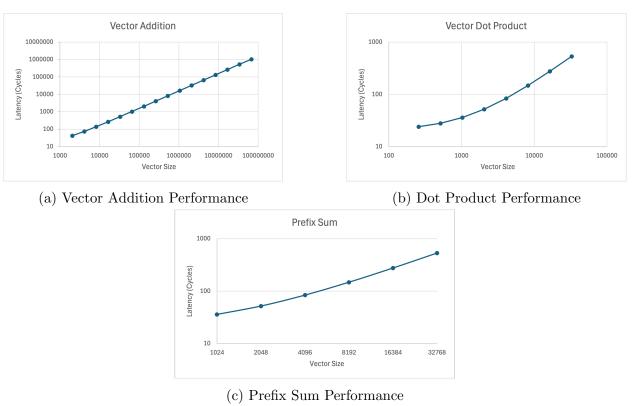

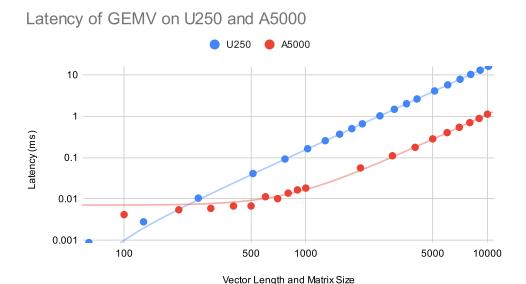

| Figure 4.1:  | DYFC BLAS performance across different operations                                                                                                                                                                                    | 107 |

| Figure 4.2:  | DYFC BLAS performance comparisons across different operations                                                                                                                                                                        | 108 |

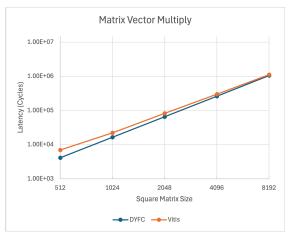

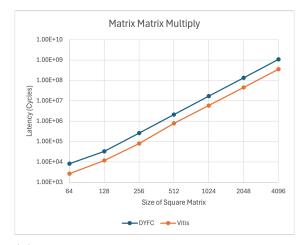

| Figure 4.3:  | Performance comparison of Matrix Vector Multiplicaton FPGA vs GPU                                                                                                                                                                    | 109 |

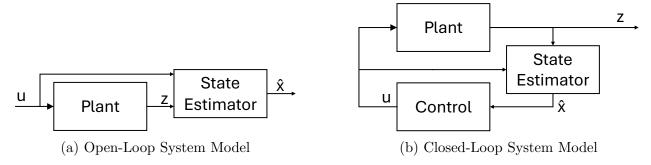

| Figure 4.4:  | System Models: Open-Loop and Closed-Loop                                                                                                                                                                                             | 117 |

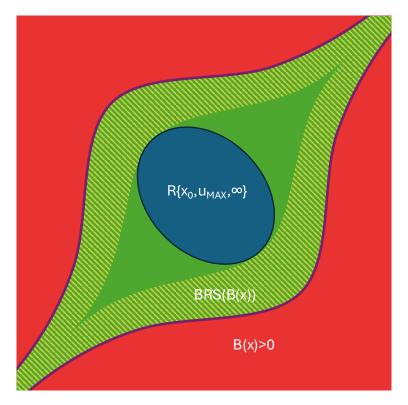

| Figure 4.5:  | $R_{\infty}$ in blue, $\mathcal{C}$ in green, $S$ in solid green, BRS in yellow, invalid points in red                                                                                                                               | 126 |

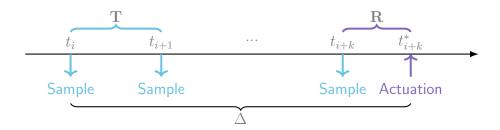

| Figure 4.6:  | Transition time over discrete sampling periods                                                                                                                                                                                       | 131 |

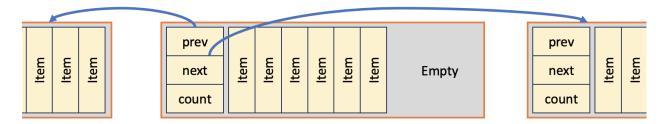

| Figure A.1:  | Structure of Hybrid Array List                                                                                                                                                                                                       | 146 |

# List of Tables

| Table 2.1: | Example Message Queue. Each column is 32 bits. Each row represents a message. | 18 |

|------------|-------------------------------------------------------------------------------|----|

| Table 3.1: | Analytical worst-case response times (ms) of our RM events executor           | 78 |

| Table 3.2: | WCET of Subtasks in Synthetic Tasksets                                        | 98 |

Acknowledgments

I would like to thank my advisor, Chris, for his guidance. I would also like to thank my

friends in St Louis who supported me, both socially and academically, in this program. A

very unique thank you to Lydia, she knows why.

Thank you to JJ, Mario, Harun, and the rest of the Dortmund group for their hospitality

and support.

A special acknowledgement is given to Allison Thackston, a roboticist I've never met, whose

ROS 2 docker templates saved me months on my dissertation.

And finally, thank you to Andrew Huey, my middleschool history teacher, who gifted me a

copy of "The Way Things Work" by David MaCaulay when I was 14. That present sent me

on the path to becoming an engineer.

This dissertation is based upon work supported by the US National Science Foundation

under grant CNS-2229290.

This dissertation contains work that has received funding by the German Federal Ministry

of Education and Research (BMBF) in the course of the 6GEM research hub under grant

number 16KISK038.

This dissertation contains content written as part of a project (PropRT) that has received

funding from the European Research Council (ERC) under the European Union's Horizon

2020 research and innovation programme (grant agreement No. 865170).

Oren Bell

Washington University in St. Louis

August 2025

viii

#### ABSTRACT OF THE DISSERTATION

Multi-Layer Support for Component-Based Cyber-Physical Systems Applications

by

#### Oren Bell

Doctor of Philosophy in Computer Engineering

Washington University in St. Louis, 2025

Professor Roger Chamberlain, Chair

Component-based design is a paradigm meant to aid in development of software applications by modularizing different functionalities of a system. This building-block approach is used extensively in cyber–physical and robotic systems. Common and established solutions to specific problems, such as perception nodes, state estimators, and motion planners, can be developed, verified, and reused as off-the-shelf modules.

These modules may be integrated atop today's heterogeneous hardware platforms, where an application can be distributed across GPUs, FPGAs, and CPU cores. When heterogeneous computational devices share the workload of a collection of components, the very act of integration may inject timing uncertainty. For example, data often must traverse different memory domains, incurring copies that may violate real-time budgets. Furthermore, the Robot Operating System (ROS) 2, the de facto middleware for robotics, has a scheduler that departs from established real-time practice, and work has only recently begun on establishing timing guarantees for it.

This dissertation builds a vertical solution that restores predictability without sacrificing modularity. The work is organized into 3 layers: memory management of hardware-accelerated devices, a real-time scheduler for ROS 2, and a control/scheduling co-design study.

Collectively, these contributions demonstrate that the promises of component-based design—modularity, compositional verification, and rapid development—can survive in the age of hardware acceleration, while still meeting cyber-physical constraints on timing and other properties end-to-end. By coupling memory-domain awareness with analyzable scheduling and timing-aware control, this work charts a practical path toward predictable, high-performance CPS and robotic systems.

# Chapter 1

# Introduction

This dissertation presents a systematic approach to designing predictable component-based real-time systems for cyber-physical applications, with a particular focus on robotics. The work emerged from a preliminary robotics project involving an autonomous drone application, which revealed fundamental challenges in achieving predictable timing. This initial exploration evolved into a comprehensive study spanning three critical layers of the system stack: memory management, scheduling, and control.

The journey began with the development of the Deer Stalker project (see Section 1.2), an autonomous drone system that highlighted the performance bottlenecks inherent in the Robot Operating System (ROS) 2 framework that this application was built on (detailed in Section 1.1). This led to the development of Hazcat (presented in Chapter 2), a memory-domain-aware communication layer. After delving into development of the ROS 2 stack, I turned my attention to the ROS 2 scheduler, which recently had been the focus of academic research highlighting its design flaws. This led to collaboration with the DAES Lab at TU Dortmund on creating real-time compliant schedulers, which is documented in Chapter 3. Finally, through collaboration with Purdue University, this research arc has culminated in a control/scheduling co-design study that demonstrates how worst-case timing analysis can be incorporated into control logic decisions that apply to other cyber-physical systems domains beyond robotics, e.g., real-time hybrid simulation in structural and mechanical engineering.

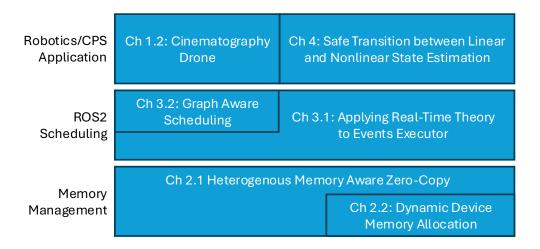

These contributions each provide different methods for building predictable real-time systems in component-based architectures. Figure 1.1 provides an illustrated breakdown of each contribution and how it fits into the system stack. Summaries of the 3 broad contributions are detailed below.

Figure 1.1: Dissertation layers

- (1) Hazcat introduces a memory-domain–aware publish/subscribe layer<sup>1</sup>. By detecting when producers and consumers reside in the same memory domain, Hazcat achieves true zero-copy, even among accelerated kernels on different components. Otherwise, it performs the minimum safe transfer. Existing middleware supports zero-copy in the CPU domain, but to our knowledge Hazcat is the only zero-copy communication middleware that supports zero-copy between accelerated kernels and also in the CPU domain. Pre-existing middleware only supports static allocations, so I also pursued the possibility of supporting dynamic memory allocation. Our particular system model violated certain assumptions that rendered existing dynamic memory allocation algorithms ineffective, so I developed a new set of dynamic memory allocation algorithms for device memory just to support Hazcat in its unique niche. Both of these contributions are described in Chapter 2.

- (2) A Real-Time ROS 2 Executor refactors the recently released events executor. My coauthors and I observed that the events executor allows for custom event queues with arbitrary behavior. We exploit this to create custom release logic. The new design is compatible with the classical periodic-task model and augments it with graph-aware, fixed-job-level priorities, addressing some of the design flaws [29] that previously plagued ROS 2. Response-time bounds are derived for arbitrary DAGs. This work is described in Chapter 3.

<sup>&</sup>lt;sup>1</sup>Publish/subscribe (pub/sub) is a communication paradigm facilitated by *topics*, which act like data queues that can have multiple writers (*publishers*) and readers (*subscribers*). Each publisher and subscriber is affiliated with only one topic. Subscribers are notified when data arrives on their topic.

(3) A Control/Scheduling Co-Design Study considers a safety-critical state-estimation pipeline that normally runs a linear Kalman Filter [70] but may switch to an Extended (or Unscented) Kalman Filter [103,119] or potentially even another kind of state estimator (e.g., a particle filter) when dynamics depart from a region of linearity. The mode-change decision explicitly incorporates worst-case timing analysis, and guarantees an upper bound on the estimation error, illustrating how control logic and real-time scheduling can be co-engineered. I also have preliminary work on implementing this project on an FPGA, and comparing its performance to a GPU. I explore the limitations and motivations of hardware-accelerated CPS applications with mixed devices. This work is described in Chapter 4.

### 1.1 ROS 2

ROS 2 is a widely adopted software framework for developing robotics applications, which has garnered significant attention from the real-time systems research community. While ROS 2 provides mechanisms for modular development, its default scheduling capabilities present challenges for predictable real-time performance, particularly for complex applications involving branching or merging data flows (i.e., arbitrary graphs).

Additional discussion on ROS 2's scheduling behavior and contributions towards improving it can be found in Chapter 3. This preface is meant to serve as a brief introduction to the ROS 2 framework and terminology, which is used throughout the dissertation.

ROS 2 provides a component-based framework for building robotic systems. Key concepts include:

- Nodes encapsulate related functionalities (e.g., sensor driver, path planner).

- Topics establish named communication channels facilitating data exchange via a publish-subscribe (pub/sub) paradigm. Nodes that provide data will *publish* to a topic, and nodes that are interested in that data will *subscribe* to it. The middle-ware responsible for the facilitation of data transfer is typically the Data Distribution Service (DDS) [45,48], although other communication protocols may be used [49,127].

- Callbacks are functions within nodes that are triggered by specific events, primarily:

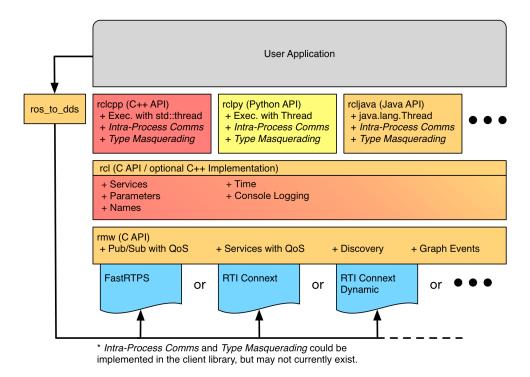

Figure 1.2: ROS 2 stack [61]

- Timer Callbacks execute periodically based on configured rates.

- Subscription Callbacks: Execute upon receiving a message on a subscribed topic.

Callbacks serve as the atomic executable units of computation in ROS 2. Through publishing and subscribing, they also can trigger each other's execution. The sequence of callbacks triggered by data flowing through topics forms the application's processing logic, often creating implicit dependencies or chains of execution. Such chains were initially defined in [29], and subsequent work [18, 20, 21, 68, 104, 110, 114] has continued using that abstraction.

ROS 2 is designed in a hierarchical stack, shown in Figure 1.2. The top layer (rclcpp, rclpy, etc) is used directly by the end-developer and provides a specific language binding to use ROS 2 with. This is where scheduling decisions are made. Without loss of generality, I will focus on rclcpp in this dissertation.

The basic functionality of ROS 2 is in the rcl layer, which provides features like nodes, namespaces, and logging.

The lowest layer of the ROS 2 stack, called the ROS Middleware (RMW) Abstraction Interface, serves as a wrapper for a communication platform, such as FastDDS [45] or CycloneDDS [48], which directly facilitates communication between nodes.

# 1.2 Preliminary Work

Before the dissertation topic was fully defined, preliminary work was done to develop an example robotics application. The application was a drone follower program, inspired by [23–25]. The application was developed in ROS 2, and was intended to be an example application for future research. Development eventually halted when performance limitations were encountered, which in turn inspired the work presented in Chapters 2 and 3. The application is detailed here, as important context and motivation for this dissertation.

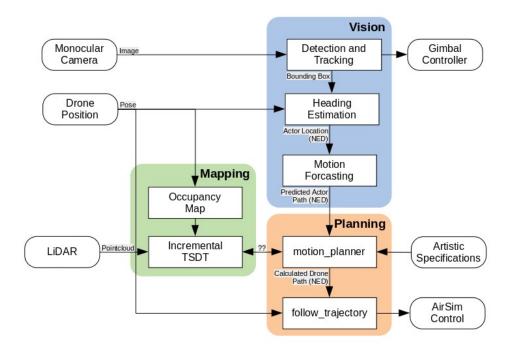

The basic structure of the application was taken from [23] and is shown in Figure 1.3. It consists of a classic sensing/planning pipeline, with a parallel pipeline for mapping. It is meant to run in AirSim [89], a robotics simulator that runs on top of the Unreal Engine [44].

In the paper that inspired our implementation, the authors intended to use the application as a platform to develop a cinematographer drone that incorporated automated cinematic decisions into its trajectory planning. It was designed to follow a moving target, such as a real-life actor. In our implementation, we had it follow a simulated deer, simply because the CGI model was free and included idling, walking, and galloping animations.

The sensing pipeline comprises 3 steps:

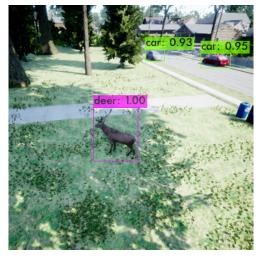

- Detection and Tracking consisted of a YOLOv4 model that detected the actor in frame, and, importantly, how far off-center it was in the frame. I had to retrain the model on images of our CGI deer, a process that was easily automated thanks to the Unreal Engine environment. A cropped bounding box of the actor was passed onto the next step. Figure 1.4a shows a still frame from the object detection step.

- **Heading Estimation** was given a tightly cropped and centered picture of the actor, with which a vision AI model would determine which direction the actor was oriented in. This task required training an original base model, but again, the collection of data

Figure 1.3: Cinematography Application [23]

was easily automated because of the Unreal Engine environment. Once the actor's position and heading were known, this was passed onto the final sensing step. Figure 1.4b shows one frame from our training set.

• Motion Estimation used a state estimator to estimate the actor's position and velocity. Assuming the drone's position is known with high certainty, the relative measurements of the actor's position and orientation from before are projected onto the ground plane, to compute the actor's position and orientation in the world frame. This is fed into a Kalman Filter to estimate the actor's position and velocity, and future trajectory. This estimation can be used to continue forecasting the actor's trajectory even when measurements aren't available, such as when the actor is occluded.

The mapping pipeline comprises 2 steps:

• Data from the Lidar and the drone's position were fused to create and expand a 3D **Occupancy Grid** of the environment.

(a) Object detection results, showing bounding boxes with labels and confidence scores

(b) Heading Estimation, model prediction in red, ground truth in green

Figure 1.4: Still frames from Deer Stalker Application

• The map data was converted into a Truncated Signed Distance Transform (**TSDT**) to create a signed distance field of the environment. The inside of obstacles are given large negative values, and the proximity just outside the obstacles are given positive values, truncated to a fixed value beyond a certain distance from the obstacle. This TSDT is passed into the planning pipeline to plan a trajectory for the drone that safely avoids obstacles.

The planning pipeline also comprises 2 steps:

• Trajectory Optimization used a path planner to plan a trajectory for the drone that safely avoids obstacles. The default path is a trajectory parallel to the actor, given a fixed distance and position for the drone (both are parameters that can be changed at runtime, if a different angle is required later in a scene). The optimization step takes this default path and adjusts it to avoid obstacles. This is done by maximizing a cost function that includes, among other components, the line integral of the trajectory computed through the TSDT from the mapping pipeline. Since the TSDT is positive in areas that avoid obstacles, optimizing this cost function will naturally push the trajectory into free space. In [24], they augment this cost function to also avoid occlusion of the actor, smoothness of the trajectory, and consistency of perspective on the actor.

• **Trajectory Tracking** is the actuation step, where the drone's position is compared to the planned trajectory, and closed loop control is used to adjust the drone's position to follow the trajectory.

This application is a compelling candidate to test future research, because it contains a diverse set of hardware-accelerable components and poses interesting challenges in system design. Before the application was fully working, I discovered one such challenge: the map data was very large, and incurred a high memory overhead when being copied from one component to another. I started investigating the possibility of using a zero-copy mechanism, which inspired the work in Chapter 2.

While developing that mechanism, I also became familiar with the ROS 2 scheduler. At the time, a paper had just been published documenting its faults [29], and I began to explore that avenue as well. Since the application consists of two chains with a merging data flow, there was naturally a need to schedule complex graphs reliably on ROS 2, which inspired the work in Chapter 3.

By the time both of those works were completed, this *deer stalker* application, as we affectionately called it, had been defunct for multiple years. The ROS 2 distro and AirSim versions it required were no longer supported, and so we sought to find a new application to which to apply the techniques developed in this dissertation. A collaboration with colleagues affiliated with the Robert L. and Terry L. Bowen Laboratory for Large-Scale Civil Engineering Research at Purdue University called for work on integrated real-time scheduling and control that could be applied to structural and mechanical engineering applications. This in turn inspired the work presented in Chapter 4.

# Chapter 2

# Zero-Copy Memory Management for Heterogeneous Computing

Real-time embedded systems support mission-critical and safety-critical applications ranging from automated and connected driving [123] to real-time hybrid simulation in earth-quake engineering experiments [46]. In recent years, the combination of component-based modularity and customizable thread and memory management in ROS 2 has made it especially attractive for developing real-time embedded robotics applications [29], including the TurtleBot 4 open-source robotics platform for education and research [34], the Hamster robust micro Autonomous Unmanned Ground Vehicle [35], and the xArm series of robotic manipulators [116].

Such systems often have timing constraints. Developers must carefully manage hardware and software overheads, timing variation, and scheduling so that real-time tasks meet their deadlines. Even atop traditional multi-core platforms, memory operations may introduce significant overheads, e.g., when the number of cores used exceeds a single chip socket so that the cost of memory operations between threads on cores in different chip sockets limits how many cores can be exploited at fine-grained time-scales [46], or when frequent communication among components causes the aggregate cost of memory operations to approach other less frequent but more expensive overheads (e.g., thread context switches). Thus, reducing the frequency of memory operations or making them more efficient [58] is an important issue for these systems.

For heterogeneous computing platforms that support hardware acceleration of computations (e.g., NVIDIA Jetson and Xilinx Kria) latency-aware memory management is even more salient. For example, it has been shown [4,97], that GPUs can be a cause of non-deterministic behaviour in real-time systems. As one particularly egregious example, memory operations on NVIDIA GPUs, particularly *cudaFree*, may cause device-wide synchronization operations

[125]. With or without hardware acceleration, a multi-component application can reduce its memory bandwidth by leveraging shared memory structures and passing references to data instead of copying the data itself [73], whenever possible. Such "zero-copy" approaches are intuitive in principle, but must enforce ownership of data to avoid race conditions, which may raise further engineering challenges in practice.

**Zero Copy in ROS 2:** Prior developments in ROS 2 have added API calls to the RMW specification that enable zero-copy through the use of borrow/return semantics. Before a publisher wishes to send data, it must *borrow* a message which it can then populate before publishing. Subscribers receive an immutable pointer to the same data, and when all subscribers have returned their pointers, the memory for the message is freed or recycled, depending on the implementation.

A popular implementation of zero-copy semantics for ROS 2 is in the Iceoryx project [49], which provides a third-party daemon that manages a shared memory pool. Publishers and subscribers wishing to make use of zero copy are required to use borrow and return semantics to access memory chunks [74] as follows:

- 1. Register the publisher and subscriber with the Iceoryx daemon, specifying their topic of interest

- 2. Borrow a chunk: the daemon returns the address of the next available block large enough to fit the message

- 3. The publisher populates the chunk with data

- 4. The publisher publishes the chunk, relinquishing ownership

- 5. Iceoryx notifies all interested subscribers of available data after which (repeatedly)

- 6. A subscriber awakes and borrows the chunk, receiving a pointer to newly available data

- 7. That subscriber processes the data

- 8. That subscriber returns their reference to the chunk

- 9. The Iceoryx daemon marks a chunk as available for reuse once all subscribers have processed it

Figure 2.1: Time sequence illustrating communication between two hardware accelerated components

Multi-core performance numbers for Iceoryx show minimal overhead [73], but Iceoryx does not support zero-copy semantics for other devices' memory: a developer wishing to leverage hardware acceleration must manually copy messages into and out of device memory. Additionally, the memory pools are pre-allocated by a third-party daemon, which the end-developer must configure to optimize memory usage. Under the default settings, memory chunks are likely to be oversized, and may not be plentiful enough to accommodate the message backlog of a worst-case scenario.

Iceoryx also only supports zero-copy of fixed-size plain-old-data types. Any messages that require dynamic allocation of memory may be partially allocated on the heap, potentially resulting in invalid pointers and segmentation faults when sharing messages between processes. This is a limitation our implementation also shares, a fix for which would likely require updates to the ROS 2 API as future work. Another zero-copy mechanism is available higher in the ROS 2 software stack [62], but it only supports intra-process zero-copy semantics. In the interest of generality, we do not assume two components share an address space so that solution is not viable for our use case.

Hardware Accelerated Workloads: Although the addition of zero-copy to ROS 2 can help to reduce nondeterminism caused by excessive memory operations, we posit that it does not go far enough. Many robotics applications leverage hardware acceleration for performance reasons, but ROS 2 zero-copy features are as yet unaware of device-memory boundaries, so components leveraging hardware acceleration must assume responsibility for copying data into, within, and out of device memory. Doing so may negate the benefits of zero copy and introduce further nondeterminism.

For components sending data to each other, we want to minimize the latency that is due to 3 types of operations, depicted in Figure 2.1: intra-component memory copies (magenta), compute operations (green), and inter-component memory copies (blue). With hardware acceleration, whether using GPUs or FPGAs, there are 3 steps: copy to device memory, run the acceleration kernel, and copy out of device memory [30,124]. These 3 operations happen within a component. We aim to remove intra-component memory copies entirely by having middleware assume responsibility for device memory operations. Inter-component memory copies also may be eliminated when conditions are right for zero-copy to occur, that is, when two consecutive nodes operate within the same memory domain.

Contributions: The Chapter covers content from two papers [13, 14]. The first paper, published at RTCSA 2023, introduces Hazcat [95]: a new zero-copy framework that supports memory domain awareness, performing contextually needed memory operations between different memory domains, and providing zero copy between two components in the same memory domain. This is covered in Section 2.1.

The second paper had an abbreviated version published at JRWRTC, the Junior Workshop for RTNS 2024. This dissertation covers the full contents of the original paper. It explores the limitations of applying dynamic memory allocation to the Hazcat framework, the challenges it poses, and new dynamic memory allocation algorithms to address them. This is covered in Section 2.2.

## 2.1 Hazcat

We introduce Hazcat [13], a new zero-copy communication middleware that supports memory domain awareness, performing contextually needed memory operations between different memory domains, and providing zero copy between two components in the same memory domain.

We use the term *memory domain* to refer to any area of memory that is tied to a particular set of processors, and is guaranteed to be readable from processors in that set: host memory is a separate domain from GPU memory, both are separate domains from FPGA memory, and data in one domain must be copied to be accessible in another domain.

We specify special heterogeneity aware (HA) allocators that manage memory for a particular memory domain, according to a domain-agnostic interface. They have functionality to access each other's memory, and perform copy operations as needed when memory contents are not in an appropriate domain. We also specify a shared message queue, analogous to a ROS 2 topic, which stores references to messages allocated by an HA allocator. Publishers put messages into the queue for later consumption by subscribers. When a subscriber expresses a preference to receive a message in a different memory domain, a copy is made on the fly in the correct memory domain and a token to the duplicate copy is also stored in the message queue. This is the worst-case scenario: when data moves across memory domains, a copy operation must occur. Each topic gets a unique message queue. Unlike Iceoryx, our system handles zero-copy in a completely decentralized manner, and developers are allowed to apply custom allocation strategies instead of being forced to use Iceoryx's static ring buffer.

Hazcat is not truly zero-copy in all circumstances. If an application is only partially hardware accelerated, memory copies will be required between portions operating in host memory and portions operating in device memory. However, if consecutive nodes operate in the same memory domain, we offer the benefits of zero-copy regardless of what that memory domain is, be it host, GPU, or (in the future) FPGA memory.

## 2.1.1 Heterogeneity Aware Allocator

Custom memory allocators are already used in real-time systems, e.g. to allocate memory statically, or to reuse previously allocated objects to avoid overheads of an operating system's default dynamic memory management mechanisms. Sophisticated features such as allocator-aware containers and polymorphic allocators [66] have been developed to allow flexible use of allocators, through which containers allocated with different strategies can be completely interoperable without subverting type-safety. A minimal allocator offers 2 functions: allocate and deallocate. Some allocators also provide object construction, but we omit this in our design: we assume that our allocators, while potentially managing peripheral device memory, will run on a CPU and should not attempt to dereference the device memory they allocate.

Managing multiple memory domains within our framework incurs stricter design requirements beyond supporting allocate and deallocate functions. We first detail a new extended interface, describe garbage collection features required whenever sharing memory, present the structure of the allocator and its memory pool, and show a way to ensure fidelity when reconstructing the allocator in other processes.

#### Allocator Interface

We propose a new allocator interface, shown in Listing 2.1, that adds functionality to convert arbitrary memory allocated by a separate allocator into a domain readable to the current allocator. This conversion may operate as a simple passthrough function if the two allocators operate in the same memory domain (this is our zero-copy condition), or it may perform the operations necessary to copy data from a separate domain.

Listing 2.1: Allocator interface for heterogeneous computing

```

class Alloc {

static int domain;

static void * create_alloc(...);

static void * remap(Alloc * alloc);

void unmap();

int allocate(int size);

void share(int offset);

void deallocate(int offset);

void * copy_from(const void* ptr, void* cpu_ptr, int size);

void * copy_to(void* ptr, const void* cpu_ptr, int size);

void * copy(const Alloc* a, void* dst, const void* src, int size);

int shmem_id;

int device_type;

int device_number;

int strategy;

};

```

Multiple allocators can be written for the same domain. We assume that any allocation can be accessed by any component in the same domain, provided any requisite memory mapping operations have been performed. The added functionality is six-fold: remap maps an allocator previously created in a different process into this process address space; unmap removes the allocator from this process address space; share increases a reference counter for a specific allocation; copy\_from copies from this allocator to a pointer in CPU memory; copy\_to copies to this allocator from CPU memory; and copy copies from an arbitrary allocator into this one, possibly going through host memory as an intermediary. Our allocators return

an integer offset rather than a pointer: allocators are mapped at different places in each process's address space, so allocations are measured relative to the beginning of the allocator and absolute pointers are recalculated in each process.

#### Deallocation and Reference Counting

Deallocation of shared memory may need to be performed by any thread: while a message is created by a publisher, whichever one of its subscribers that holds the reference last is responsible for deallocation.

For time-sensitive threads, deallocation must be a time-bounded operation, which limits the types of allocation strategies we can use. For now, we only provide a static ring buffer and intend to provide additional options in the future, but stipulate that all allocation strategies must offer O(1) deallocation.

We assume that every memory domain is copyable into host memory and vice-versa. However, not every memory domain may be copyable into each other, so each allocator must specify *copy\_from*, to copy memory from itself into host memory, and *copy\_to*, to copy memory to itself from host memory. The *copy* function is often a wrapper for those two steps in sequence: copying from the source domain to host memory, and then from host memory to the target domain. However, depending on available hardware, developers may code special conditions that bypass host memory, e.g., for GPU-GPU copies.

An HA allocator must implement a reference counting strategy, so the *deallocate* function will not free an allocation until it is called more times than there have been calls to *share* the same allocation. Note this creates a race condition that is resolved by the message queue as discussed in Section 2.1.3. When implementing new allocators for device memory, the allocator methods cannot access the memory they are allocating, so strategies like boundary tags [76] are not applicable.

Allocators provide additional information: device\_type identifies the hardware device the allocator is managing memory for; for multiple instances of that device\_type, device\_number can distinguish them; and strategy identifies the allocator approach, such as ring buffers, TLSF [88], or best-fit [76]. Two allocators' device\_type and device\_number must be the same to take advantage of zero copy, with device\_type and strategy used to perform function

lookups when an allocator is mapped into a new process, based on its ID according to System V shared memory (a POSIX standard that creates unique system-wide IDs for different shared memory segments).

#### Allocator Structure

Each allocator comprises 3 contiguous memory mappings: a local portion, a shared portion visible across processes, and a pool of mapped device memory. The local portion stores function pointers as a way to emulate the convenience of object-oriented polymorphism, which we use so that our message queue does not need to concern itself with type information. True polymorphism is not possible for objects in shared memory, due to uncertainty of the structure of some data types, which combined with inherent type-erasure that occurs during inter-process communication would prevent us from knowing the structure of an allocator created in another process. The goal is for different allocator implementations to have an identical structure in their first few bytes, so we use plain-old-data structures for our allocator design to guarantee this.

Since function pointers are not valid across process boundaries, the allocator portion that holds them is not a shared mapping.

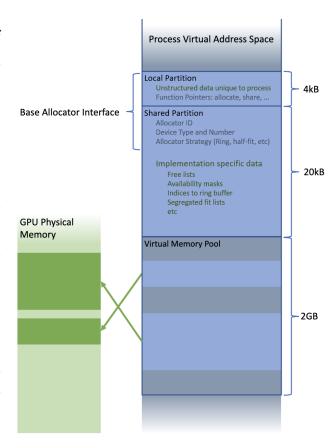

Figure 2.2: Structure of allocator and partitions (not to scale)

This leads to a design in which our allocator object straddles different memory mappings, the bulk of which is visible across processes, with the local partition only visible to the current process. Due to granularity requirements, a minimum of 4kB is allotted to the local partition, but only 56 bytes are needed for the 7 non-static function pointers. The remainder

is unstructured space that may be used as appropriate for the convenience of the allocator implementation. The start of the allocator's shared portion contains required type information that is relevant when remapping it into a new process, using the new allocator interface described above in Listing 2.1. The rest of the shared mapping varies by implementation. After the shared mapping is the actual memory pool, often mapped in device memory, which again varies by implementation. For dynamic allocators, it's useful to start with an arbitrarily large virtual memory pool unbacked by physical memory. This gives the allocator room to grow, while still guaranteeing it can be reconstructed in a different process.

#### Reconstructability of Allocators

Reconstructibility is essential: since allocators are not guaranteed to start at the same virtual memory address in different processes, memory allocations are expressed in terms of offsets from the start of their allocator and the relative structure of the allocator and its memory pool must be identical between processes. This is complicated by alignment restrictions on shared memory for different devices and systems. The minimum size of the local partition is a page (typically 4kB). The granularity of shared memory varies (4kB on x64 systems, but 16kB on ARM), as does the required granularity of device memory.

The allocator is only reconstructible in a location that satisfies all these granularity requirements. The shared mapping must end at an address that's a multiple of the shared granularity. Similarly, the device mapping must start at an address that's a multiple of the device granularity. Since the shared mapping and the device mapping are contiguous, then the boundary between them must be at an address that is a multiple of the least-common-multiple of both their granularities:

$$lcm(m,n) (2.1)$$

We make an initial reservation of unmapped virtual memory at approximate location  $\hat{x}$  of size

$$a + b + c + lcm(m, n) \tag{2.2}$$

That is, the collective sizes of the local, shared, and device mappings, plus a buffer zone to align it correctly. A valid position satisfying all granularity constraints is guaranteed to exist in any memory range of this size. If the boundary of shared and device memory partitions must be at a multiple of lcm(m, n), then some modular arithmetic reveals that our reservation x must start at

$$\hat{x} + \operatorname{lcm}(m, n) - ((x + a + b) \mod \operatorname{lcm}(m, n)) \tag{2.3}$$

Any virtual memory before this point or past the tail can be released. Virtual memory within this range will be remapped to local, shared, and device memory in contiguous blocks guaranteed to begin at an address that satisfies their granularity requirements.

| Metadata  |            |       | Mem Domain 1 |             |             | Mem Domain 2 |             |             |

|-----------|------------|-------|--------------|-------------|-------------|--------------|-------------|-------------|

| Sub Count | Avail Bits | Locks | Alloc ID     | Offset      | Size        | Alloc ID     | Offset      | Size        |

| 0         | 0          | 0     | ~            | ~           | ~           | ~            | ~           | >           |

| 1         | b11        | b10   | 0x0000 0014  | 0x0000 D0F8 | 0x0001 4100 | 0x0000 001A  | 0x0000 04D0 | 0x0001 4100 |

| 3         | b10        | ь00   | 0x0000 0015  | 0x0021 0A00 | 0x0000 0B00 | ~            | ~           | ~           |

| 3         | b10        | b11   | 0x0000 0014  | 0x0001 21F8 | 0x0001 4100 | ~            | ~           | ~           |

| ***       |            |       |              |             |             |              |             |             |

Table 2.1: Example Message Queue. Each column is 32 bits. Each row represents a message.

## 2.1.2 Message Queue

In a publish/subscribe application, topics can be modelled as queues of messages. This is because execution of subscription processing may be delayed and a backlog of work may accumulate. In soft real-time systems, a queue can have a maximum length and stale messages may be dropped.

In our framework, these message queues exist as named shared memory files, with the name taken from the topic name. In ROS 2, topics are named with strings. So a ROS 2 topic named /perception/rear\_camera would be saved as a shared file with the name:

When using Hazcat outside of ROS 2, these message queues can be named arbitrarily. The structure and example contents of a message queue are shown in Table 2.1. We describe the formatting of this design, and the methods for interacting with it, including registration and the *publish / take* calls.

#### Design of a Message Queue

Each message is stored in the queue in three parts: an allocator ID, the memory offset, and the message length. The allocator ID is used to look up an allocator, which may or may not be mapped already into the current process. These mapping operations typically occur once near the beginning of a program's run. After an allocator is mapped into the process's address space, the memory offset is added to the allocator's starting address to get the absolute address of the message. Each message may have multiple copies, one for each memory domain. The entire message queue is then structured as a collection of arrays: one per memory domain, plus an extra array for metadata.

The message length is a latent design decision for now. As mentioned in Section 2.1.1, we only support fixed-size plain-old-data datatypes for messages, so specifying message length is redundant, as it could be inferred from the topic. In the future, however, we plan to implement support for zero-copy of dynamically sized messages.

Each entry in the metadata array contains 96 bits, as follows. 32 bits serve as a subscriber counter to indicate if the message is still in use. 32 more bits serve as an availability map for up to the 32 supported memory domains, where a 0 indicates the message hasn't been copied to this domain, and a 1 indicates it is ready for zero-copy reading. The last 32 bits serve as locks for each memory domain to prevent redundant copy operations from colliding.

This allows up to 4 billion publishers and subscribers per topic, and 32 supported memory domains. The zero-th memory domain will always be host memory, but the rest are assigned

in order of registration and have no relation to the *device\_type* or *device\_number* mentioned above in Section 2.1.1.

In addition to the message queue itself, there is header data (not illustrated) to track the size of the message queue, the number of registered memory domains, and a global iterator pointing to the most recent message index. Subscribers also store their own iterator to the most recent message they haven't yet read. The sub counter tracks how many registered subscribers haven't read the affiliated message yet. Whenever a subscriber takes a message (covered in Section 2.1.2 on the *take* command), the sub count is decremented.

#### Publisher and Subscriber Registration

Before interacting with the message queue, a publisher or subscriber must register with Hazcat. A publisher or subscriber can only be affiliated with a single topic which they request during registration. The associated message queue will be mapped into the current process (or created from scratch). Pursuant to the subscriber's requested backlog, the message queue may be resized. Other processes will be informed of this when they attempt to fetch data and note the message queue's self-reported size does not match the size of their own mapping, at which point they remap the message queue with its larger capacity.<sup>2</sup>. We assume that all publishers and subscribers are registered during an application's initialization phase, so these resizing operations will not be a part of steady state operation.

When the application terminates, publishers and subscribers are also required to unregister, which is largely just decrementing an entity count. The last process to unregister the last of the publishers and subscribers for a message queue will also destroy the message queue.

When resizing message queues for topics, we consider the design philosophy behind ROS 2 when developing Quality of Service (QoS) policies [60]. The general principle is that publishers offer a quality of service, and subscribers request a quality of service. Since we are not concerned with packet loss over a network, the ability of publishers to retain a message history for resending is unnecessary. Thus, only the requests of the subscribers are relevant and the message queue should be the largest depth of all interested subscribers.

<sup>&</sup>lt;sup>2</sup>In practice, this resizing would seldom occur, due to the shared memory object being page aligned. A 4kB page is enough to hold tokens for well over 60 messages across 4 different memory domains. Few applications would require more than this.

Since shared memory objects must be page aligned, the minimum footprint is still large enough to accommodate over 60 backlogged messages across 4 memory domains. 4 arrays of 96 bit entries, plus another metadata array of 96 bit entries, makes 60 bytes per entry. A 4kB page then equates to 68 entries.

#### Publish command

The *publish* command is called by a publisher with a message to publish. First, it atomically fetches and increments the index of the next available row. It then secures a lock on the entire row, which ensures that any subsequent attempt to modify that row will block until the current call finishes.

If there are any remaining messages in that row (due to wrap around of the message queue) they are deallocated. This dropping of messages will only occur if there are best-effort components in the system, which are assumed to be tardy and unaffected by the missed messages. Any hard real-time tasks have to consider this deallocation as a source of interference when computing their response time. In a well-designed application with only hard real-time components, the message queue would never overflow, as an accumulated backlog exceeding the quality-of-service setting is by definition a system failure. The alloc id, offset, and size fields illustrated in Table 2.1 are updated accordingly and then the write lock is removed. Finally, a signal is sent on the associated FIFO to inform other processes that a message is available.

#### Take command

The *take* command is called by a subscriber after being notified that a message was available (a convenience, not a required step). First, the row for the oldest unread message is found. If the subscriber is up-to-date and no new messages are available, the call returns NULL. After inspecting the availability bitmask for the row, if the message is available in the subscriber's preferred domain, it will *share* the message and then prepare to return it. If the message isn't available in the message's preferred domain, an available copy is identified and the entry for that is fetched. The subscriber's allocator then allocates a new message and performs a copy operation as shown below in Listing 2.2.

This new message copy is also stored in the row with the original, the availability mask is updated accordingly, and the allocator ID and message offset are prepared to be returned. Whether or not a copy occured, one last check is made. If this subscriber is the last to access this message, the message queue will release its references to all copies of this message across all domains, potentially deallocating some if no other subscribers hold a reference. Messages with a non-zero reference count remain available to access for any subscriber that is already running. When they finish, they also decrement their reference count and the last to finish deallocates the copy in their particular domain. This does mean that subscribers frequently use messages that are no longer tracked by the message queue. We do this because tracking message ownership in the message queue requires locking a message reference as read-only until all subscriptions return. These locks would provide an opportunity for best-effort subscriptions to indefinitely block a real-time publisher trying to submit a message, which is unacceptable, so we require our HA allocators to implement reference counting themselves.

```

alloc = lookup(sub.alloc_id)

src_alloc = lookup(entry.alloc_id)

msg = src_alloc + entry.offset

len = entry.len

here = alloc.allocate(len)

if (CPU == src_alloc.domain) {

alloc.copy_to(here, msg, len)

} else if (CPU == alloc.domain) {

src_alloc.copy_from(msg, here, len)

} else {

alloc.copy(here, src_alloc, msg, len)

}

```

Listing 2.2: Copy a message into the preferred domain when zero-copy conditions are not met

### 2.1.3 Message Lifecycle

As a recap to our system design, we cover the steps to create, use, and dispose of a message. We conclude with comments on thread safety and steps to prevent race conditions for shared memory. The steps to interact with Hazcat are 4-part: allocate, publish, take, and deallocate.

The *allocate* method is called on an allocator to create memory for the message, as detailed in Section 2.1.1. During a component's computation, the message is populated.

After the first component is finished, it calls *publish*, which places the allocator ID and message offset in the relevant message queue, as described in 2.1.2.

When a second subscribed component has been informed of a message, it calls *take*. This modifies the message queue as described in Section 2.1.2 and also affects the messages directly: it calls *share* on the message copy in the component's memory domain, which increments the reference counter stored in the allocator. If this subscriber is the last to read the message, it will also call *deallocate* on all the message copies, which decrements the reference counter. This is akin to clearing the message queue's references to the message copies.

The message won't be garbage collected until this subscribed component calls *deallocate* one more time to clear it's own reference to the message, which is the final step.

In Section 2.1.1, we mention that the *share* and *deallocate* commands create a natural race condition. This is resolved by the fact that *share* is only ever called from within the *take* command, while the message is owned by the message queue. Calling *deallocate* from a separate thread concurrently with the *take* command is always guaranteed to do nothing, as the message queue itself retains a reference to the message. The only circumstance where calling *deallocate* will truly deallocate a message is when the message is no longer tracked by the message queue, so there's no possibility of *share* being called on it simultaneously.

### 2.1.4 Design and Implementation

Any component-based framework using a CORBA or pub/sub communication model can be modified to use Hazcat as its communication layer. Calls can be made to Hazcat to register publishers and subscribers, create messages, publish to a topic, take from a topic, and finally deallocate messages. All that is needed is a translation layer to incorporate this into a desired framework.

For sake of demonstration, we created an RMW to interface with ROS 2 systems and provide these zero-copy benefits to ROS 2 applications. We also provided 2 allocators, one each for CPU and GPU, both implementing a static ring buffer. Additional allocators can be added readily in the future, such as one for the real-time dynamic memory strategy TLSF [88].

These allocators can be specified by the end developer when instantiating publishers or subscribers. These are done through the use of subscription\_options and publisher\_options, which each contain a field called rmw\_implementation\_payload. This mechanism can be used to pass options specific to an RMW implementation, in this case a Hazcat allocator. If this field is ignored, then a default CPU-based allocator is assumed.

When extending the Hazcat platform to new products and hardware, we make certain stipulations for features the drivers must provide: an IPC mechanism to share device memory allocations with unrelated processes; support for unified-virtual-addressing, including virtual memory reservations; and mapping of physical memory to an explicit virtual address, subject to page granularity constraints.

First, the hardware driver must implement some interprocess communication (IPC) mechanism for its device memory. Any device memory allocated must be able to be accessed by any unrelated process using a globally unique token. Depending on how this mechanism is implemented, or whether it's implemented at all, may naturally limit a product's performance and its viability to be used with Hazcat. As an illustrative example, CUDA now provides shareable handles for IPC communication with their new driver API calls. As of CUDA 10.2, a developer can use cuMemExportToShareableHandle and cuMemImportFromShareableHandle to create a handle allegedly shareable between processes. However, these calls only work for related processes. The shareable handles are process-specific file descriptors, and any attempt to translate these descriptors to another process, via the procfs and the new pidfd\_getfd syscall, will inevitably fail. Why this happens is not explained in the current CUDA documentation. The handle is intended to be used before a fork() operation, and is not conducive to IPC between arbitrary processes.

Additionally, the drivers for the hardware device in question must support unified-virtual-addressing. Remapping allocators requires concatenating shared memory with device memory in a way that they appear as a single object. While their absolute location may vary, their relative positioning must be intact between processes. Thus, once a shared memory mapping is created for the allocator, its device memory pool must be placed in a particular location in a process's address space. If this ability is not present, we can't make guarantees about the positional relationship between an allocator and its memory pool. These guarantees are essential to correctly locate messages using nothing more than an offset.

Lastly, to avoid race conditions when claiming address space, the device needs a call to reserve virtual memory. The allocator and device memory then can be mapped in without another thread claiming adjacent virtual memory.

CUDA's driver APIs support all the necessary virtual memory features mentioned above, but lack an adequete IPC mechanism. The traditional CUDA API does not support address reservations and explicit memory mapping, but does have IPC functionality that meets our constraints. However, the two APIs provided are not compatible. We can conclude that based on the aggregate functionality present in both APIs, NVIDIA hardware has the capability to work with Hazcat, but as it stands, Hazcat cannot support CUDA on it for independent-process workloads. The experiments below in Section 2.1.5 therefore use components in a single process or in related processes.

### 2.1.5 Empirical Evaluation

#### Two Component Experiments

As a demonstrative example, we evaluate a sample application with two nodes. Each performs a simple bilateral filter on a random 4k image, to serve as an arbitrary parallelizable computation. These experiments were performed on a desktop system with an AMD Ryzen7 3700X CPU and an NVIDIA RTX 2070 Super. We measure the end-to-end latency and perform stacktrace sampling on this application while it runs on three different middlewares: CycloneDDS, Iceoryx, and our Hazcat.

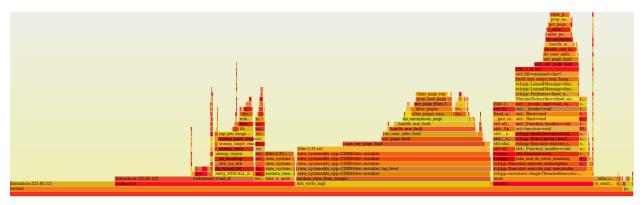

(a) CycloneDDS Flame Graph (end-to-end latency: 50.8ms)

(b) Iceoryx Flame Graph (end-to-end latency: 27.2ms)

page remove...

top per sage...

sample gage real

sample gage real

sample gage real

do group exit |

do group exit |

get sage...

| linearly sect...

| linearly s

(c) Hazcat Flame Graph (end-to-end latency: 13.7ms)

Figure 2.3: Stacktrace Sampling

Figure 2.4: Two Component Experiment with Hardware Acceleration

Due to the limitations of CUDA IPC mentioned in Section 2.1.4, these nodes were run in the separate threads in the same process, instead of in different processes, though we expect that the performance differences with that other case would be negligible. We measure the steady state operation of the system, so the first 1 or 2 samples were dismissed as outliers if their runtime latencies differed significantly from the subsfequent samples. Such outliers were seen in the Iceoryx uniprocessor example, as well as in all of the GPU examples (presumably due to kernel loading).

Figure 2.1 illustrates the different operations performed by this two-component sample application. Each operation type is detailed in Section 2, and mean timing information for each variation is illustrated in Figure 2.4. Variation in the end-to-end latency for all three middlewares is displayed in the violin graphs in Figure 2.5. These figures were created by manually placing userspace probes in the application to measure timing at the entry and exit points for GPU memory operations, GPU kernels, and the callback functions for each component.

Stacktrace sampling can be found in Figures 2.3a, 2.3b, and 2.3c. The width of these flame graphs has been normalized according to their respective end-to-end latencies, so the time spent in each function can be better visualized.

Our tracing tools are unfortunately incapable of extracting stack traces from within CUDA code, so any uses, be it from kernel execution or memory operations, are combined into "libcuda". We observe that CycloneDDS and Iceoryx spend roughly the same amount of

Figure 2.5: End-to-end Latency Distributions for Two Component Experiment

time in the CUDA library, independent of their other sources of overhead. Hazcat, however, spends much less time running CUDA code. Since the three are running the same kernel, we can assume time spent on GPU computation remains constant, and the variation observed is a result of reduced GPU memory operations.

We see this confirmed in Figure 2.4. Trials with Iceoryx see reduced latency compared to CycloneDDS, despite running the same code. This is because of CycloneDDS's worse overhead and required memory copies between components (as dissected in 2.3a). Hazcat runs slightly modified code, where the memory copies in userspace have been removed. Almost all of the end-to-end latency under Hazcat is from GPU computation.

The Iceoryx and Hazcat variations both implement some type of zero copy and as a result have reduced inter-component (and even intra-component) latency – the latter is due to performing a *publish* call on the underlying middleware while the node is running. This call performs a memory copy in CycloneDDS but has minimal overhead in Iceoryx and Hazcat.

CycloneDDS and Iceoryx incur the overhead of additional GPU memory operations when using hardware acceleration. This is the primary performance benefit of Hazcat over Iceoryx: eliminating unnecessary GPU memory operations.

Figure 2.5 shows density plots of the end-to-end latency of each experiment variation. The distributions on the hardware accelerated workloads show that both Hazcat and Iceoryx have tight lower bounds, highlighting that with them the best case is the typical case.

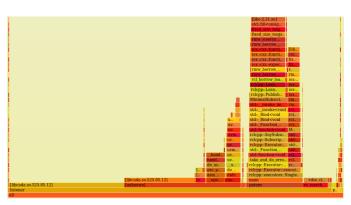

Figure 2.6: Relative performance with randomized ROS graphs

CycloneDDS, with its higher overhead and excess inter-component memory copies, sees more variation.

The most interesting finding is that Hazcat also has a tight upper bound. Iceoryx's use of GPU memory copies creates a source of latency jitter. Hazcat, on the other hand, has no such issue, making it behave much more predictably compared to the other two frameworks.

## Synthetic ROS Graphs

To demonstrate Hazcat's performance in more complex workloads, we synthetically generated 98 ROS graphs with randomized message sizes for topics and randomized CPU or GPU computation for nodes. Graphs ranged from 2 to 14 nodes, 1 to 17 edges, and had critical paths ranging from 2 nodes to 5.

Each graph was run using Hazcat, Iceoryx, and CycloneDDS, and their end-to-end latencies were measured. The first three samples were discarded from each run, to eliminate outliers caused by transient effects during startup or shutdown.

Different graphs will naturally have vastly varying end-to-end latencies. We observed mean latencies ranging from 15 to 206ms. Since plotting all 98 graphs would be infeasible, measurements were instead normalized. For each graph, performance was measured as the deviation from the mean latency of that graph observed on Iceoryx. That is, if 3 runs of the same graph on Iceoryx take 10ms, 12ms, and 17ms (mean of 13ms), each run will then be plotted in Figure 2.6 as -3ms, -1ms, and 4ms. If a run of the same graph on Hazcat takes 8ms, it will be plotted as -5ms.

Hazcat had a better mean performance than CycloneDDS for every graph. It performed comparably ( $\pm 10\%$ ) with Iceoryx for 60% of the graphs, and out-performed Iceoryx for 9% of the graphs.

When examining individual graphs, we notice that Hazcat performs comparably to Iceoryx in graphs dominated by CPU work, as well as graphs with wide work but a short span. Such graphs comprised the majority of our test set. The largest performance benefits come when multiple successive GPU nodes are chained together, and can benefit from the device-memory zero copy.

There was a greater deal of temporal variance in Hazcat, which we ascribe to its experimental implementation.

## 2.1.6 Conclusions and Future Work

The primary contribution of Hazcat's heterogeneity aware zero-copy features for heterogeneous computing environments is that memory copies are only performed when data in one memory domain is needed in a different domain. In all other cases, memory is recycled, drastically reducing the worst case end-to-end latency of an application as well as removing sources of nondeterminism.

In our synthetic benchmarks with randomized ROS graphs, we saw an average case speedup of 1-73% over the unoptimized CycloneDDS middleware, depending on the graph in question, with 27% being typical. When compared to Iceoryx, we observed anywhere between nearly a 1.8x slowdown to a 2x speedup, again, depending heavily on the graph in question.

The largest performance benefits are mostly seen when consecutive components in the application all operate in the same domain. Even in the worst case, for an application using n domains, we never saw more than n-1 copy operations per message.

We observe that in addition to performance gains in hardware acceleration workloads, our framework has a decentralized design, which additionally reduces the requisite developer knowledge, as there is no 3rd party daemon to launch and no ring buffers to configure. Built-in defaults and runtime initialization allow it to perform well even when limited information is provided about the application.

One obvious avenue of future work is to support a wider range of hardware. Here, we only discuss CUDA based usage of NVIDIA hardware, but FPGAs are an important target for future research as well. Given the aforementioned lapses in the CUDA drivers' support of IPC, we plan to investigate other approaches to support GPUs [30] [97].

As a motivating application to test Hazcat's usefulness in the ROS 2 ecosystem, it is proposed to modify the Autoware Realtime Benchmark [1] to provide CUDA support. Then, an empirical comparison can be made between ROS 2 applications running on Iceoryx vs Hazcat.

# Zero Copy with non-POD Message Types

Previously stated, the biggest competitor to Hazcat is Iceoryx, an interprocess zero-copy communication middleware. One of the main limitations of Iceoryx is only being able to support Plain-Old-Data (POD) message types<sup>3</sup>. That is, data allocations with a fixed size known at allocation time and no recursive elements, as is typical with object-oriented programming. Currently, Hazcat also shares this limitation.

The ability to allocate an object and then decide the size of a member array at a later point has obvious benefits from a programatical standpoint. But the ability to support a message comprised of multiple allocations has an additional benefit when working with device memory: the ability to spread a message across memory domains.

<sup>&</sup>lt;sup>3</sup>In the time between when the Hazcat paper [13] was published and when this dissertation was written, the developers of Iceoryx have attempted to address this exact feature and determined there was not sufficient industry interest to justify complicating their design. This suggests support for non-POD message types is at present primarily of academic interest, but this discussion is left in the dissertation for completeness.

For instance, when storing an image in ROS 2, the message type contains not only the image data, but also a header, containing metadata such as dimensions and encoding information. If the image data is to be processed on a hardware-accelerated device, this header data would provide valuable information to pass to the kernel launch, or determine whether the kernel should even be executed.

Enabling these kind of hybrid-compute applications motivates Hazcat as a useful player in the middleware space.